- 文:Wa-People/李慧臻 Jane Lee

- 圖:Wa-People/編輯中心

- 2022.02.22

圖說:西門子加入英特爾晶圓代工服務計劃 EDA 聯盟西門子數位化工業軟體近日宣布加入成為英特爾晶圓代工服務(IFS)加速計劃中的 EDA 聯盟特許成員。該計劃旨在建立完備的生態系統,基於 IFS 先進的製程技術,為新一代系統單晶片提供設計與製造支援。聯盟内的合作夥伴可提前取用英特爾製程與封裝技術,共同最佳化並增進工具和流程,以充分利用英特爾的技術能力。

- 文:Wa-People/李慧臻 Jane Lee

- 圖:Wa-People/編輯中心

- 2022.01.13

圖說:新思科技SiliconSmart 元件庫特性解決方案,獲台積電 N5、N4 和 N3 先進製程的認證。 新思科技近日宣佈其SiliconSmart元件庫特性解決方案已獲得台積N5、N4和N3製程技術的認證。該解決方案具備了支援先進節點的單位元件庫特性所需的強化功能,能加速行動/5G、高效能運算、AI、汽車、互聯網網路以及航太和國防應用的數位實作。

- 錄影/製作:產業人物影音中心

- 2021.12.15

圖說:Cadence 台灣區總經理宋栢安與人力資源部資深經理 Elena在《竹科四十,為年輕人說故事》特刊及影片中,為年輕人說故事。2020年產業人物特刊《竹科四十,為年輕人說故事》專訪了 Cadence台灣區總經理宋栢安與人力資源部資深經理 Elena,宋栢安總經理分享他如何找到志向,加入產業,並在產業磨練成長,他也為年輕人勾勒未來發展的機會; Elena資深經理介紹獲得台灣最佳職場(GPTW)的Cadence,並且透露她在面試新鮮人的時候,最在意的是什麼。

- 文:Wa-People/李慧臻 Jane Lee

- 圖:Wa-People/編輯中心

- 2021.12.02

圖說:Cadence獲台積電2021四項開放創新平台 (OIP) 年度合作夥伴大獎,推動3DFabric設計、雲端解決方案、4nm 設計架構的共同開發以及DSP矽智財創新。Cadence資深副總裁暨數位與簽核事業群總經理滕晉慶博士表示:「藉由Cadence與台積電持續的合作,我們使共同客戶能夠利用我們的最新技術自信地交付設計並實現設計目標。獲得台積電四項大獎殊榮彰顯了 Cadence 藉由其智慧系統設計策略致力於實現卓越的 SoC 設計。」

- 文:Wa-People/李慧臻 Jane Lee

- 圖:Wa-People/編輯中心

- 2021.11.30

圖說:經濟部部長王美花於11月12日頒發「創新應用夥伴獎」給台灣新思科技總經理李明哲(右)。 台灣新思科技近日獲經濟部頒發「電子資訊國際夥伴績優廠商 - 創新應用夥伴獎」,以表揚新思科技配合政府推動人工智慧、物聯網等產業合作,協助台灣產業不斷創新,對促進台灣的產業發展具有卓越貢獻。這是該公司對於協助推動台灣的人工智慧產業發展,首度獲經濟部的肯定。台灣新思科技總經理李明哲表示,新思科技是全球領先的EDA與介面IP廠商,也是台灣半導體產業發展的重要策略夥伴。

- 文:Wa-People/李慧臻 Jane Lee

- 圖:Wa-People/編輯中心

- 2021.11.25

圖說:國研院半導體中心主任葉文冠(Wa-People資料照,攝影:古榮豐)為因應國際半導體技術發展趨勢,科技部轄下國家實驗研究院台灣半導體研究中心與新思科技日前簽訂合約,引進該公司Sentaurus TCAD與Quantum ATK模擬工具,提供台灣學術界免費使用,讓台灣學術界享有與產業界同步的半導體製程研發環境,以加速開發下世代關鍵半導體製程技術,並培育優質人才。

- 文:Wa-People/李慧臻 Jane Lee

- 圖:Wa-People/編輯中心

- 2021.11.23

圖說:台灣新思科技總經理李明哲(右)領取「全球企業永續獎(GCSA)」之永續報告銀牌獎新思科技(Synopsys)近日獲頒「全球企業永續獎(GCSA)」之永續報告銀牌獎(Sustainability Report, Silver Class),肯定該公司在企業經營之外,持續深耕台灣、追求零碳排放的未來、致力營造包容與多樣(inclusion & diversity)的企業文化 、及善盡企業公民責任(Corporate Social Responsibility),尤其疫情期間主動在公司內部成立防疫小組,積極守護並促進員工的身心健康。

- 文:Wa-People/李慧臻 Jane Lee

- 圖:Cadence

- 2021.11.10

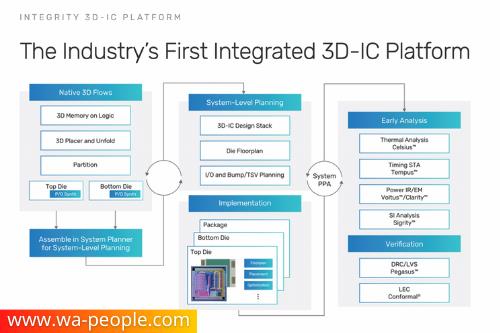

圖說:Cadence 以完整3D-IC平台支持台積電 3DFabric技術,加速多晶片設計創新。Cadence宣布正與台積電緊密合作加速 3D-IC 多晶片設計創新,作為合作的一部分,Cadence Integrity 3D-IC 平台是業界第一個用於 3D-IC 設計規劃、設計實現和系統分析的完整統一平台,支持台積電 3DFabric 技術,即台積電的 3D 矽堆疊和先進封裝的系列技術。此外,Cadence Tempus 時序簽核解決方案已優化升級,支持新的堆疊靜態時序分析 (STA) 簽核方法,從而縮短設計周轉時間。