- 文:Wa-People/王麗娟 Janet Wang

- 錄影/製作:產業人物影音中心

- 2019.05.13

圖說:產業人物主筆王麗娟專訪Synopsys設計事業群聯席總經理 Deirdre Hanford新思科技(Synopsys)使用者大會(SNUG)2019年參加人數超過800人,討論議題幾乎全面性涵蓋了所有IC設計的挑戰。Fusion(融合設計平台)、縮短設計時間的方法,讓設計更快更有生產力、加快上市時程及彈性。Synopsys設計事業群聯席總經理 Deirdre Hanford出席SNUG Taiwan 2019研討會,產業人物主筆王麗娟專訪Deirdre Hanford,介紹Fusion 設計平台投片已超過100個產品。

- 文:Wa-People/王麗娟 Janet Wang

- 圖:Wa-People/李慧臻 Jane Lee

- 2019.05.10

圖說:Synopsys設計事業群聯席總經理 Deirdre Hanford出席SNUG Taiwan 2019研討會,介紹Fusion 設計平台投片已超過100個產品。新思科技(Synopsys)SNUG Taiwan 2019研討會主打融合設計平台(Fusion Desigh Platfrom)可以加快設計速度,協助客戶掌握人工智慧及物聯網世代的新一波產業浪潮。Synopsys設計事業群聯席總經理 Deirdre Hanford指出,Fusion Desigh Platfrom推出第一年就已經有超過100個產品成功投片,寫下7奈米的重要里程碑。

- 文 / 圖:Wa-People/李慧臻 Jane Lee

- 2019.05.08

圖說: 新思科技數位與客製化設計平台,獲台積公司5奈米FinFET製程技術的認證。新思科技近日宣布,針對台積公司領先業界的5奈米FinFET製程技術,新思科技的數位與客製化設計平台已通過其最新的生產就緒(production-ready)設計規則手冊(Design Rule Manual,DRM)的認證。該項認證經過多次的測試晶片投片(test chips taped out),且目前多家客戶正用以進行生產設計(production design)的開發,能協助實現各種高效能運算、高密度到低功耗行動應用等晶片設計。此項認證乃植基於雙方多年來的廣泛合作與嚴格的驗證。

- 文:Wa-People/ 編輯中心

- 圖:Wa-People/攝影團隊

- 2019.05.01

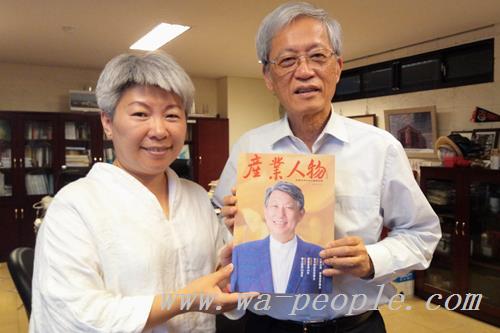

圖說:產業人物主筆王麗娟(左)贈送前工研院院長暨董事長史欽泰2019產業人物雜誌 。(攝影:李慧臻)2019產業人物雜誌出版了。包括台積電創辦人張忠謀退休後最重要的一場演講、華立集團張瑞欽董事長以材料與設備支持台灣工業發展五十年、前工研院顯示中心程章林主任貢獻產業四十年後將幫助年輕人視為志業,還有為國際一流大廠導入零氣泡封裝技術、首次接受媒體專訪的印能創辦人洪誌宏,皆是雜誌亮點。

- 文 / 圖:Wa-People/李慧臻 Jane Lee

- 2019.04.16

圖說:新思科技推出新款embARC機器學習推論(Machine Learning Inference)軟體庫,針對使用卷積神經網路(convolutional neural networks,CNN)和循環神經網路(recurrent neural networks,RNN)的低功耗IoT應用進行最佳化。新思科技近日宣布推出新的embARC機器學習推論軟體庫,當SoC開發人員採用新思科技DesignWare ARC EM 和HS DSP 處理器IP、進行高效能神經網路SoC設計時,可大幅提升開發效能。embARC MLI軟體庫提供開發人優化的功能,可於神經網路各層階中執行。

- 文:Wa-People/李慧臻 Jane Lee

- 圖:Wa-People/編輯中心

- 2019.04.11

圖說:Cadence推出Clarity 3D求解器,為系統分析設計處理提供,以及前所未有的容量與功能。全球電子設計創新領導廠商益華電腦宣佈以Cadence Clarity 3D求解器進軍快速成長的系統分析與設計市場。Clarity 3D求解器模擬速度提升多達10倍,處理容量無限,且具備黃金標準精度。其運用最新分散式多進程技術,有效解決在晶片、封裝、PCB、連接器和纜線上規劃複雜3D結構設計時所面臨的電磁問題—以桌機、高性能運算或雲端運算資源協助工程人員進行真正的3D分析。

- 文 / 圖:Wa-People/李慧臻 Jane Lee

- 2019.03.29

圖說:新思科技啟動「AIoT設計實驗室」產學合作計劃。左起成功大學電機系主任謝明得、交通大學副校長陳信宏、新思科技全球副總裁暨台灣區總經理李明哲、科技部政務次長許有進、新思科技總裁暨共同執行長陳志寬、國研院台灣半導體研究中心主任葉文冠、清華大學特聘講座教授吳誠文、台灣大學電子工程研究所所長吳安宇、中央大學研發長顏上堯。新思科技宣布與台灣大學、清華大學、交通大學、中央大學以及成功大學等學校共同啟動「AIoT設計實驗室」產學合作計劃,捐贈各校晶片開發核心套件與人工智慧/機器學習教材,培育先進半導體設計人才。