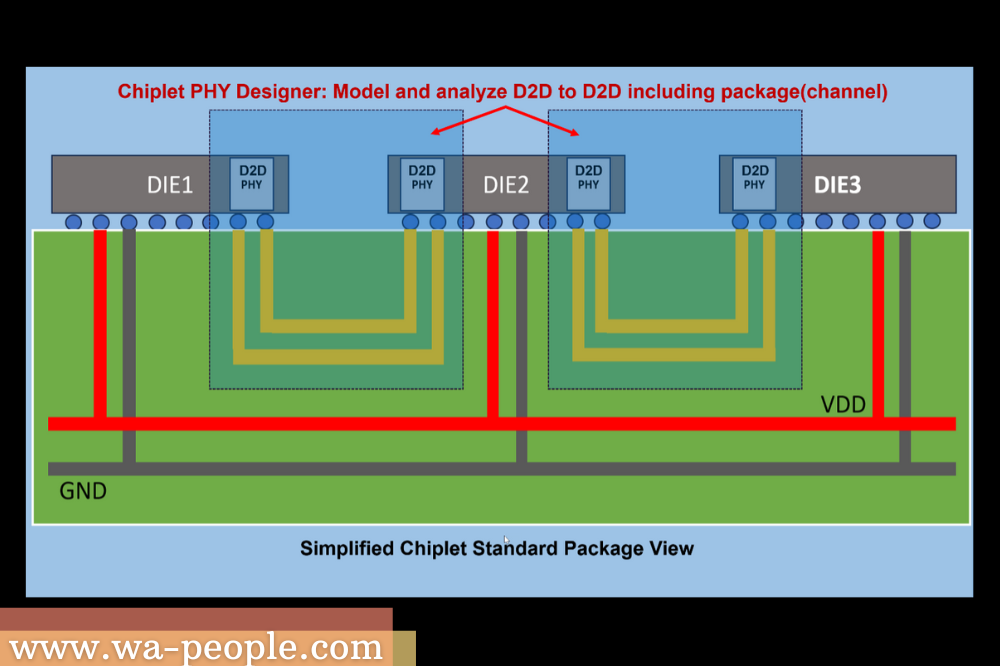

圖說:是德科技Chiplet PHY Designer可根據UCIe規格模擬D2D實體層互連。

是德科技(Keysight )日前宣布推出Chiplet PHY Designer,這是該公司高速數位設計與模擬工具系列的最新成員,提供晶粒間(D2D)互連模擬功能,可對業界稱為小晶片(Chiplet)之異質和3D積體電路(IC)設計的效能進行全面驗證。新的電子設計自動化(EDA)工具提供業界首創的深度建模和模擬功能,讓小晶片設計人員能夠快速準確地驗證其設計是否符合通用小晶片互連(UCIe)標準的規格。

UCIe已成為半導體產業最重要的小晶片互連規格。這個開放標準定義了先進2.5D或3D封裝中小晶片的互連方式。許多頂尖的半導體設備和EDA工具供應商,以及晶圓廠和小晶片設計工程師,都已開始支援或採用UCIe標準。當更多設計人員使用此互連標準,來確保其小晶片的效能符合規格,業界便可建立一個致力於實現小晶片互通性和商業化的廣泛生態系統。

過去數十年間,是德科技EDA研發團隊一直投入於對符合產業規格的高速數位介面進行建模和模擬。舉例而言,ADS Memory Designer軟體具備IBIS-AMI建模功能,可提供包含GDDR7、DDR5、LPDDR5和HBM3等完善的記憶體介面。其嚴格且真正的JEDEC相符性測試解決方案,使用與Keysight Infinium示波器系列相同的測試演算法,可處理100多個測試ID。

Chiplet PHY Designer實體層模擬器的主要特色包括:

- 支援UCIe實體層標準 – 自動解析信號然後根據標準慣例進行命名、透過封裝互連在多個晶粒間自動連接、標準所驅動的模擬設定,例如速度等級,以及透過專用的探針元件進行直覺性的量測設定。

- 電壓轉移函數(VTF)量測 – 可精確計算VTF以確保符合UCIe規格要求,可分析低至1e-27或1e-32位準的系統誤碼率(BER)。可量測眼圖高度、眼圖寬度、時脈偏差、遮罩邊限和BER輪廓。

- 可分析前向時脈(forwarded clocking),以便準確地擷取非同步時脈特性。

是德科技EDA事業群副總裁暨總經理Niels Faché表示:「我們的高速數位模擬團隊深知SerDes實體層所帶來的左移(Shift Left)挑戰。現在,他們將這些多年經驗應用於小晶片領域,成功地將是德科技基於標準的模擬策略推展到UCIe。互連建模對於系統設計和效能至關重要。Chiplet PHY Designer可在設計週期的早期,從一個D2D實體層,透過互連通道連到另一個D2D實體層,來加速驗證小晶片子系統。它可協助3D IC設計工程師解決關鍵的互連效能問題,並改善預測性虛擬原型設計,讓業者能夠搶占市場先機。」