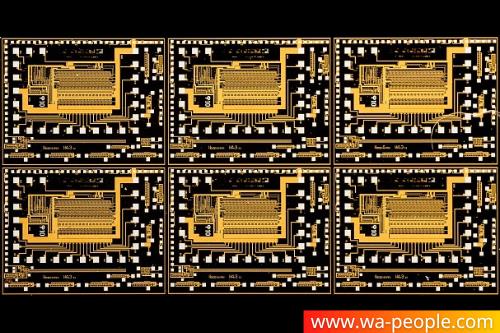

圖說:西門子 Calibre 平台擴充早期設計驗證解決方案

西門子數位化工業軟體近期為其積體電路(IC)實體驗證平台 —— Calibre 擴充了一系列電子設計自動化(EDA)早期設計驗證功能,可將實體和電路驗證任務「shift left」,既在設計與驗證流程的早期階段就識別、分析並解決複雜的 IC 和晶片級系統(SoC)實體驗證問題,協助 IC 設計團隊及公司更快將晶片送交光罩製造(tapeout)。

在設計週期的早期識別並解決問題不僅有助於壓縮整個驗證週期,還能提供更多時間和機會來改善最終設計的品質。西門子使用合格的簽核(signoff)要求,為早期分析、驗證與最佳化策略提供經過調整的檢查支援,讓設計公司能簡化設計流程、提高設計師的生產力並縮短上市時間。

西門子 EDA Calibre 設計解決方案產品管理副總裁 Michael Buehler-Garcia 表示:「要在 EDA 領域保持技術領導地位,必須深入瞭解客戶在日常工作中面臨的特定挑戰,並在這些挑戰的驅動下持續進行改進。透過在 Calibre 中增添早期設計驗證功能,使我們的客戶無論處於哪一個設計階段,都可使用最新技術,將世界級的矽晶產品迅速推出市面。」

Calibre nmPlatform 工具套件在 EDA 產業中獨具優勢,其整合了各種主流的 IC 設計與佈局實作工具。這種無縫整合的特點,使設計團隊能從於智慧財產(IP)、區塊/巨集和全晶片層級輕鬆運用 Calibre 工具,這些工具都從其客製化設計或佈局與佈線(P&R)設計環境中執行。此外,Calibre 平台還具備獨特的檢視與除錯能力,可加快各設計階段的速度。