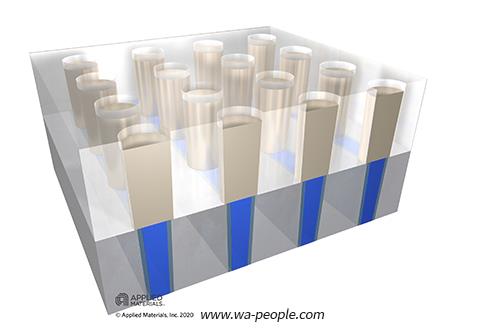

圖說:應用材料發表鎢製程技術,可解決邏輯晶圓代工節點中持續平面(2D)微縮所面臨的重要瓶頸。

應用材料推出新式的選擇性鎢(Selective Tungsten) 製程技術,可提供晶片廠商以新的方式構建電晶體觸點,這是連結電晶體與晶片中其他電路非常關鍵的第一層電路。該創新的選擇性沉積技術能降低影響電晶體性能並增加耗電量的接觸電阻。透過這項技術,電晶體的節點微縮與觸點能縮小至5奈米、3奈米甚至更小,並同步提升晶片功率、性能與面積/成本(chip power, performance and area/cost, PPAC)。

微縮挑戰

雖然微影技術的進步可有效縮減電晶體觸點通孔的大小,但使用金屬填滿通孔的傳統作法仍會嚴重影響PPAC。傳統上,電晶體觸點是以多層方式形成。首先,接觸通孔是先襯上黏著層和氮化鈦阻障層,接著利用沉積技術產生成核層,最後再使用鎢來填滿剩餘空間。鎢因其低電阻係數成為接觸金屬的首選。

7奈米製程技術的接觸通孔直徑只有20奈米。襯墊/阻障層與成核層就佔了75%的通孔體積,只剩下25%供鎢使用。細薄的鎢線具有很高的接觸電阻,會嚴重影響PPAC與2D微縮效果。

VLSIresearch董事長暨執行長Dan Hutcheson表示:「EUV的興起使得我們必須解決一些重大的材料工程挑戰,以持續進行2D微縮。襯墊阻障層就像是這個產業的動脈硬化斑,不斷阻撓晶片中的電子流動,以至於無法達到頂尖的性能。應用材料的選擇性鎢技術正是我們夢寐以求的創新突破。」

選擇性鎢沉積

應用材料的全新Endura Volta 選擇性鎢化學氣相沉積系統,能讓晶片製造商在電晶體的接觸點通孔內進行鎢的選擇性沉積,以消除線性/阻障層及成核層。整個通孔會充滿低電阻鎢,並解除後續PPAC的瓶頸。

應用材料的選擇性鎢沉積技術是一項整合材料解決方案,在純淨、超高真空環境中結合多重製程科技,比無塵室本身還要潔淨許多倍。原子層表面處理可應用於晶圓,採用獨特的沉積製程,讓鎢原子在接觸點通孔內選擇性沉積,形成無分層、無縫、無間隙自下而上的完美填充。

應用材料半導體產品事業群副總裁凱文.莫瑞斯(Kevin Moraes) 指出:「數十年來,業界只能仰賴2D微縮來推動功率、性能、面積、成本方面的同步改善。然而,現今尺寸變得如此之小,傳統材料以及材料工程技術也遇到物理極限。我們的選擇性鎢整合材料解決方案,是應用材料在不影響功率與性能前提下所推出新微縮方法的發明,也是一項絕佳的代表之作。」

全球已有多家領先客戶採用全新的 Endura 系統。這是應用材料在創新沉積製程技術方面的最新力作;其他產品組合包括選擇性磊晶 (selective epitaxy)、選擇性沉積 (selective deposition) 以及選擇性移除 (selective removal)。這些選擇性製程能讓晶片製造商運用全新方法製作、形塑並調整材料,以便持續在 PPAC 精進。